Electronics | Free Full-Text | VR-ZYCAP: A Versatile Resourse-Level ICAP Controller for ZYNQ SOC | HTML

Electronics | Free Full-Text | VR-ZYCAP: A Versatile Resourse-Level ICAP Controller for ZYNQ SOC | HTML

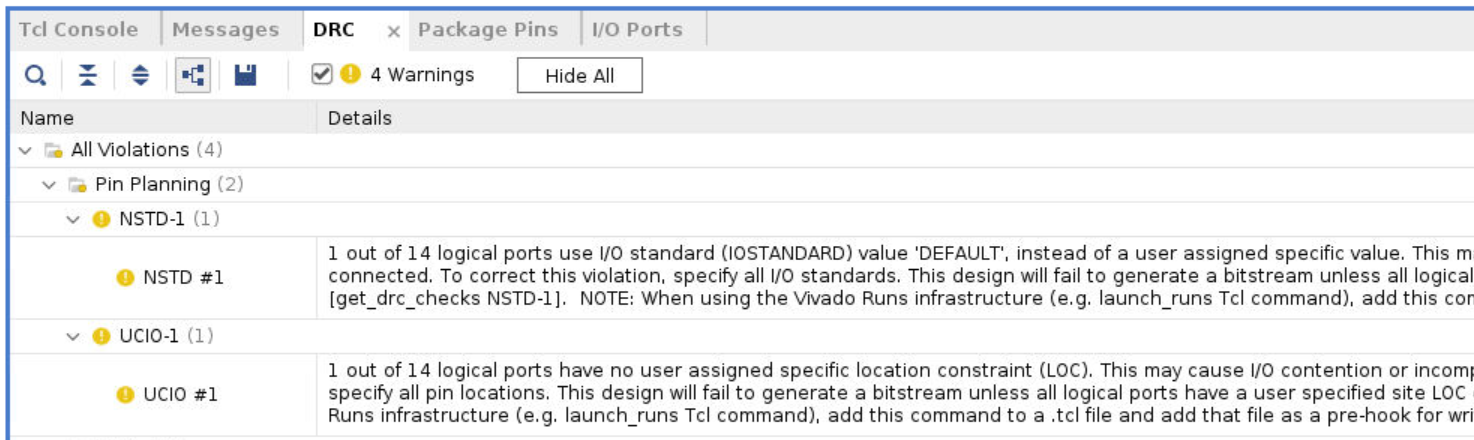

56354 - Vivado write_bitstream - ERROR: [Drc 23-20] Rule violation (NSTD-1) Unspecified I/O Standard - X out of Y logical ports use I/O standard (IOSTANDARD) value 'DEFAULT', instead of a user assigned specific value