Fine resolution delay tuning method to improve the linearity of an unbalanced time‐to‐digital converter on a Xilinx FPGA - Berrima - 2020 - IET Circuits, Devices & Systems - Wiley Online Library

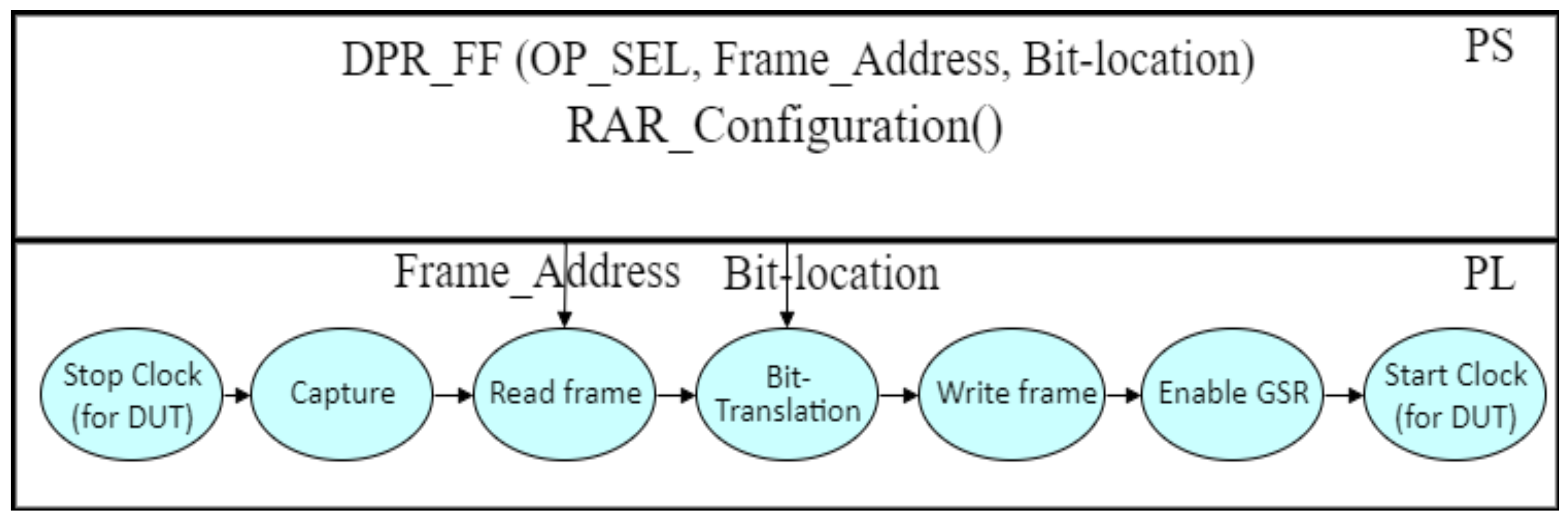

Electronics | Free Full-Text | VR-ZYCAP: A Versatile Resourse-Level ICAP Controller for ZYNQ SOC | HTML

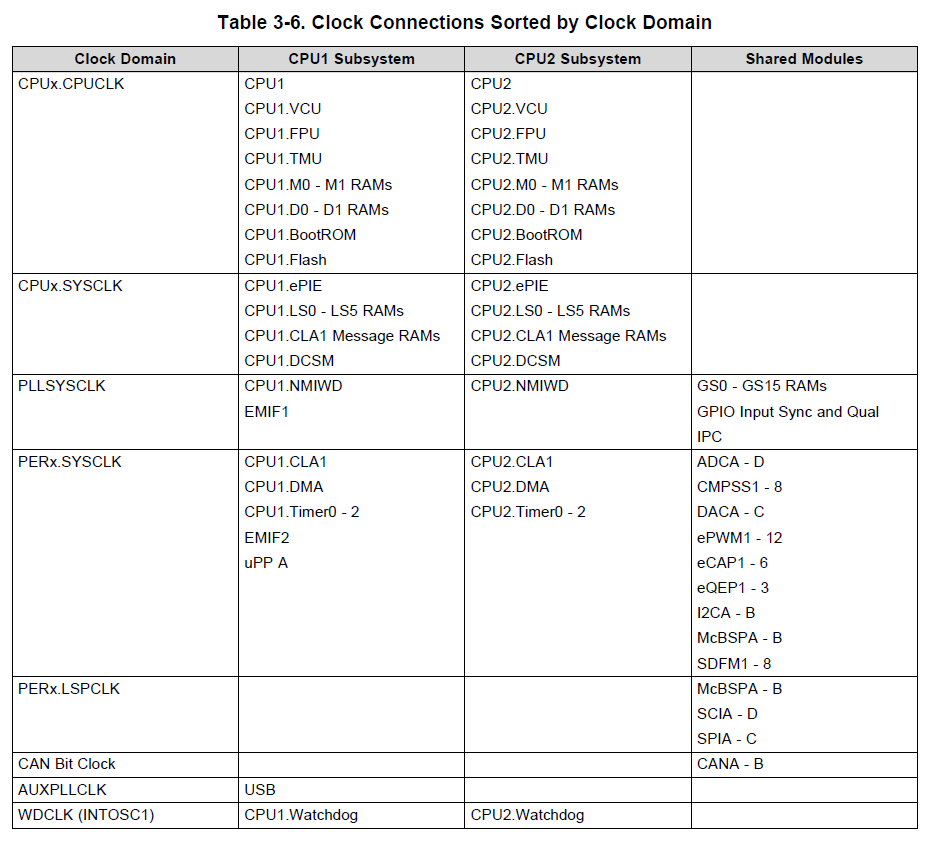

CCS/LAUNCHXL-F28379D: CLB clocking - Code Composer Studio forum - Code Composer Studio™︎ - TI E2E support forums

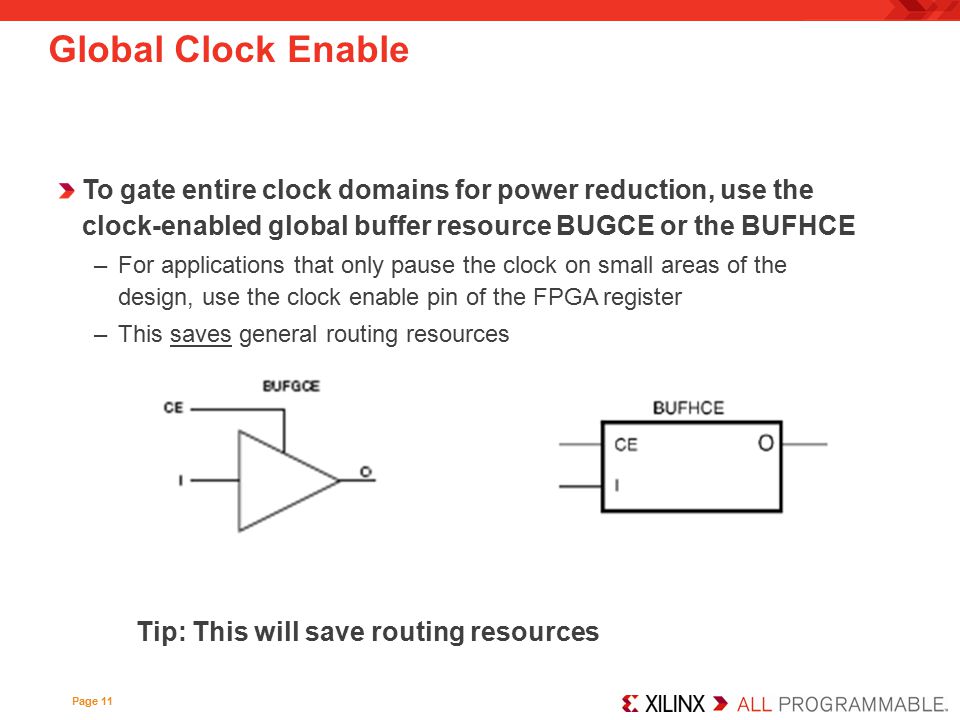

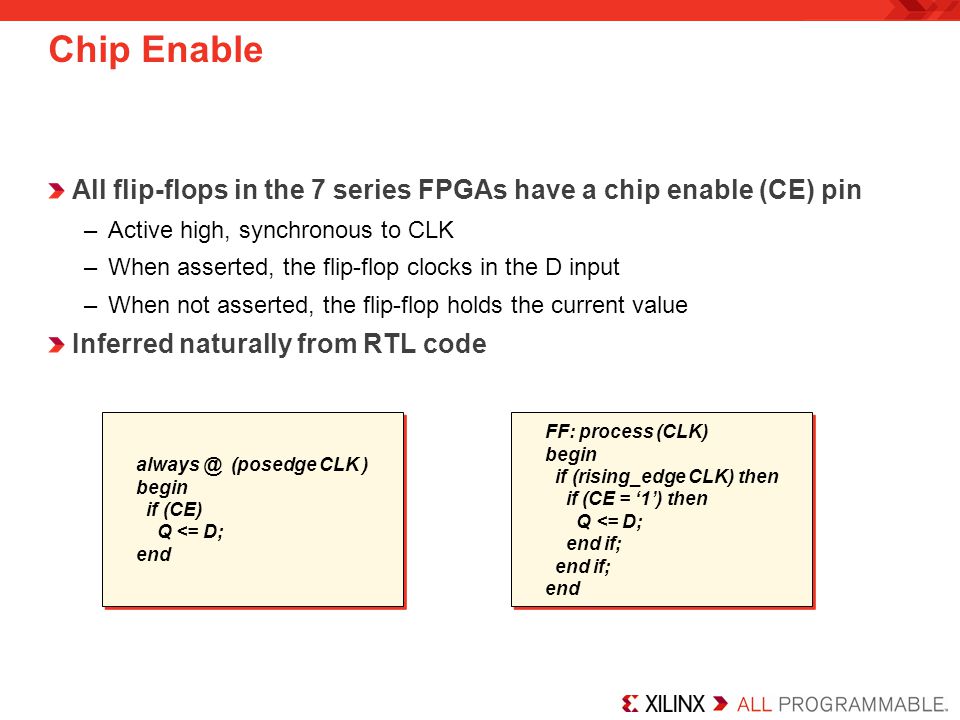

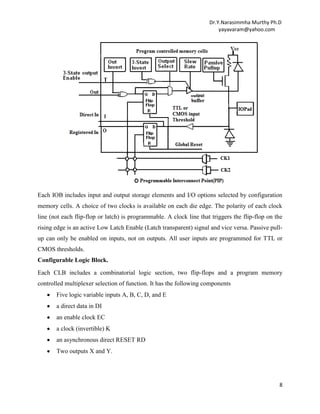

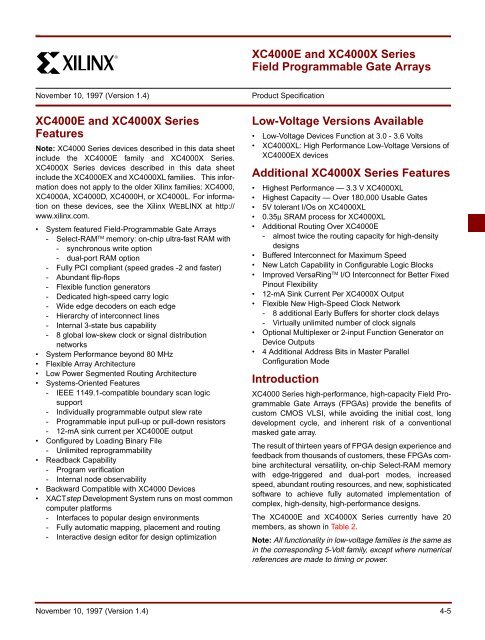

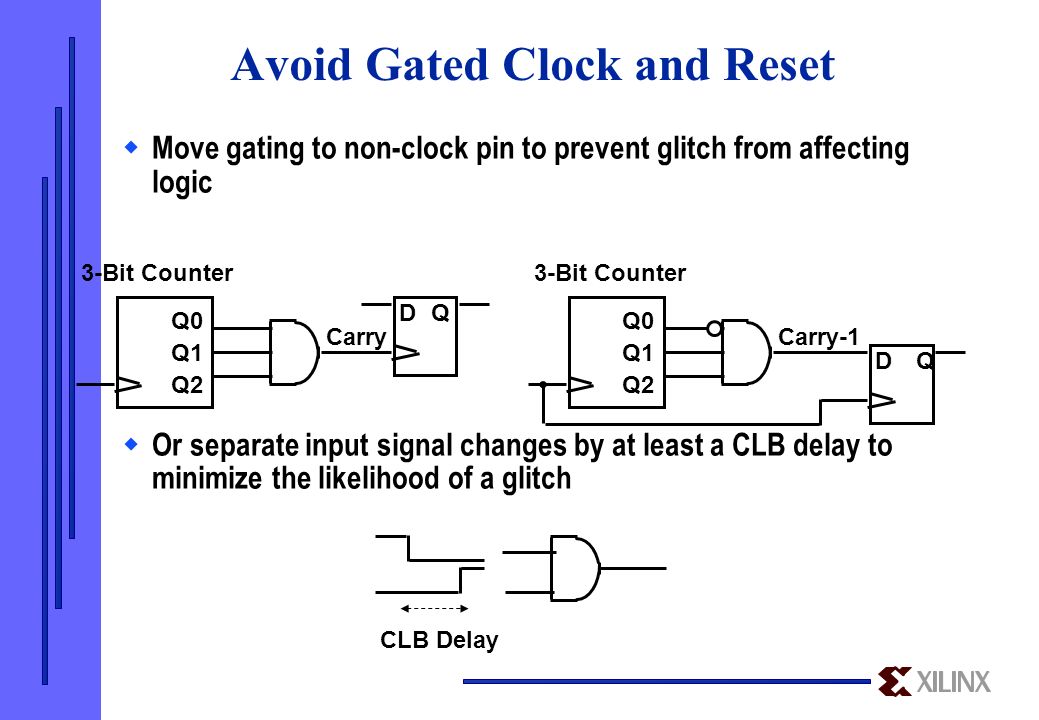

Useful Design Guide To Make the PLD. Xilinx FPGA Gate Count Standardized on Logic Cell as unit of measure Maximum capacity = number of logic cells. - ppt download