Design and Implementation of Efficient FIR Filter Structures using Xilinx System Generator | Semantic Scholar

Design and Implementation of Efficient FIR Filter Structures using Xilinx System Generator | Semantic Scholar

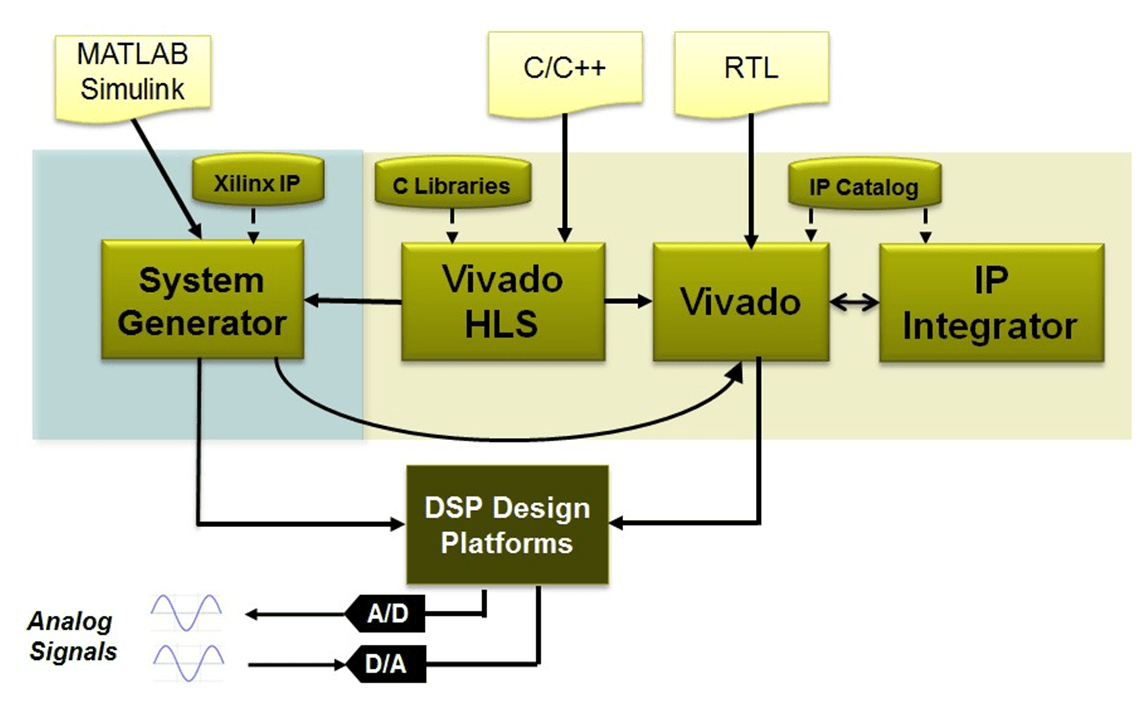

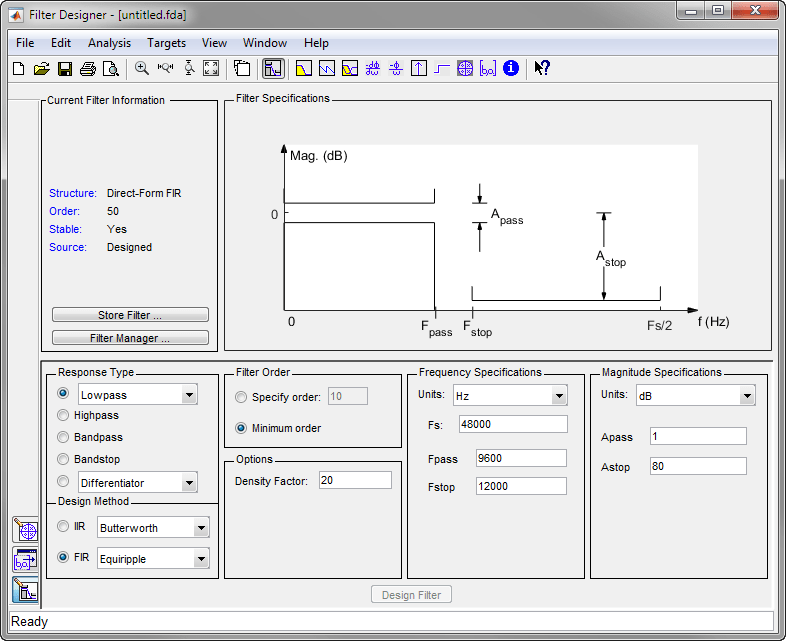

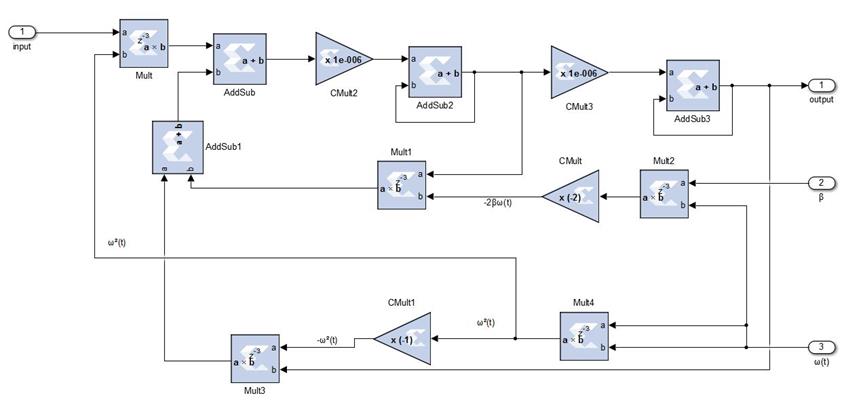

Design and Implementation of Low-Pass, High-Pass and Band-Pass Finite Impulse Response (FIR) Filters Using FPGA